Intel Announces 7th Gen Kaby Lake: 14nm PLUS, Six Notebook SKUs, Desktop coming in January

by Ganesh T S & Ian Cutress on August 30, 2016 9:00 AM EST- Posted in

- CPUs

- Intel

- 14nm

- Kaby Lake

- Gen 9

- Speed Shift

- Turbo Boost

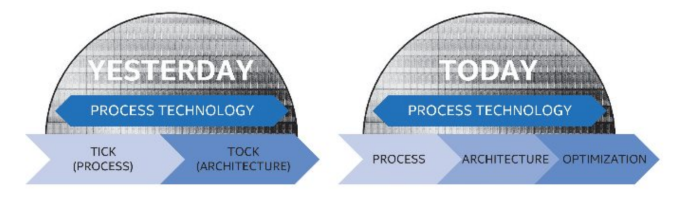

When Intel first announced the shift from the dual-stage ‘Tick-Tock’ methodology that had driven their core CPU design teams for over a decade into the three-way ‘Process, Architecture, Optimization’ paradigm, there were questions as to how much of the final stage, the Optimization, would actually change the way CPUs were presented or offer upgrades in performance. At the time, ‘Kaby Lake’ as the name for Intel’s third crack at their 14nm process was well known, but users wondered if it was just another Devil’s Canyon (better overclocking) or a full on CPU launch. Well the answer is the latter, and the launch is staggered between today and January. Roll on Kaby Lake. Is that Kah-bee Lake, or Kay-bee Lake?

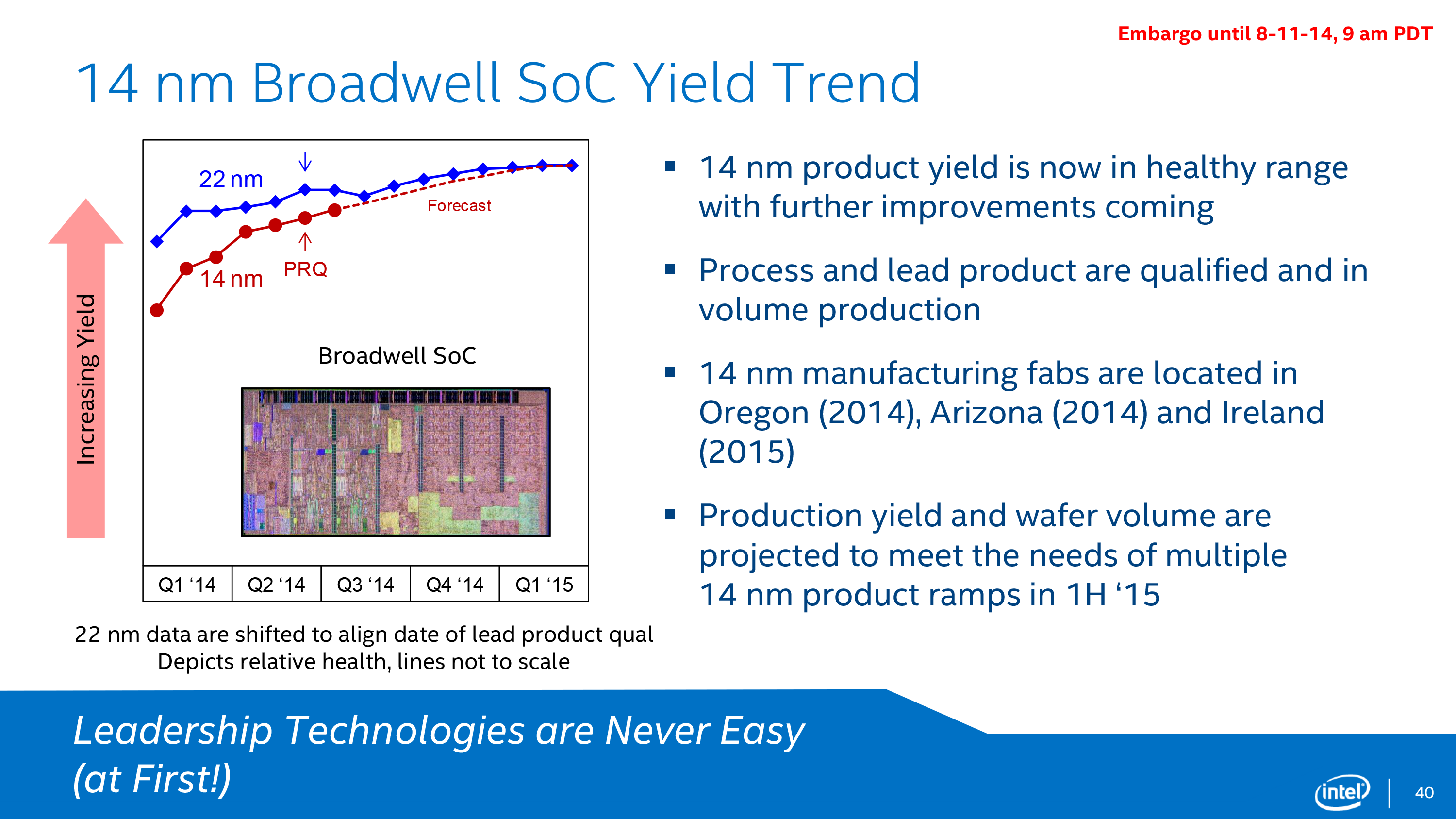

Tick-Tock to Process-Architecture-Optimization (PAO)

Intel’s two year processor cadence of Tick-Tock allowed the company to alternate reducing the lithography node (a tick) with an upgraded microarchitecture (a tock) with modest gains of performance. Each stage of the Tick-Tock would take 12-15 months, with new lithography nodes taking longer and longer to reach maturity. Eventually it has gotten to a point where 14nm took too long to become pervasive in Intel’s product stack. For a manufacturing company and a CPU company, slowly rolling out Broadwell notebook and low power parts and then gutting the mid-range desktop was the result of the troubles of bringing 14nm to the prime time. Now in 2016 we have the launch of full-sized Broadwell-EP server parts running up to 22 cores in a 145W envelope, but the low power parts are a couple of microarchitectures ahead. We have this strange situation of a stretched landscape, partially driven by markets but also for manufacturing.

The move from Intel’s 14nm process to 10nm is a long, slow burn, taking much longer to develop than any process previous. We first saw 14nm in Broadwell mobile CPUs in Q3 of 2014, almost two years ago, and 10nm still isn’t on any public roadmap for early 2017. With the tick-tock strategy, and the launch of Skylake in mid-2015, this would leave Intel without a new CPU launch for almost two years, which is unheard of from Intel. Also, Intel’s partners rely on product cycles to announce and launch new products to generate revenue. To fill the gap, plus with a few other techniques, Intel moved to Process-Architecture-Optimization, or PAO for short.

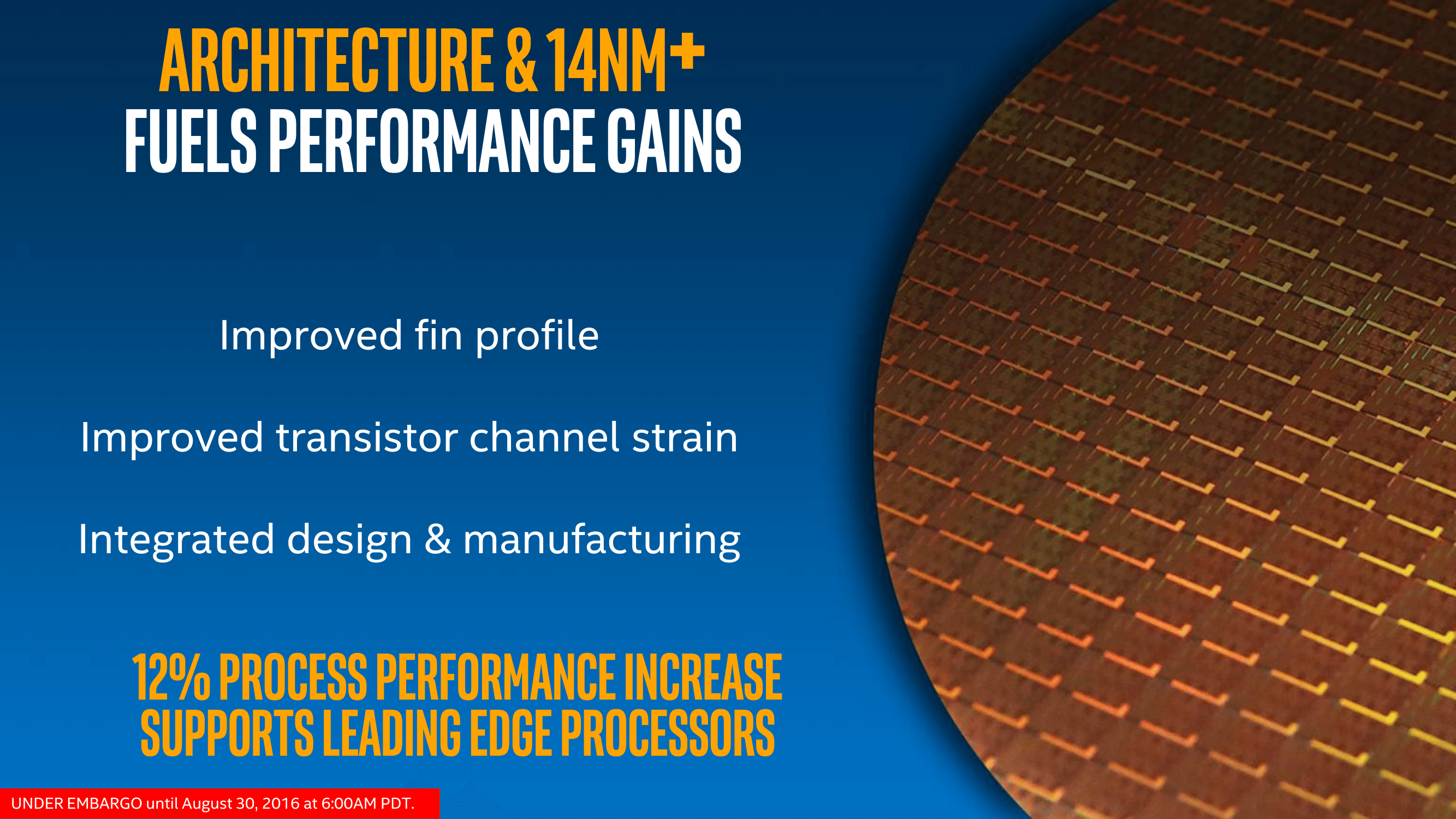

This means three bites of the cherry for 14nm before we see 10nm in prime time. First it was Broadwell, then Skylake, and today Intel is announcing Kaby Lake. As part of the release, Intel has mentioned that a number of key benefits for Kaby Lake will be based on an optimized 14nm process, called 14PLUS (or 14nm+, 14FF+). This process as a quick summary has a higher fin height and larger pitch, essentially giving a less-dense set of transistors that have more room to breathe. Normally a larger pitch means more voltage required, but this is offset by the fin height and Intel says is good for another few hundred MHz for performance. The less-dense design, in theory, may also help in overclocking, however we will have to wait until January to see those results.

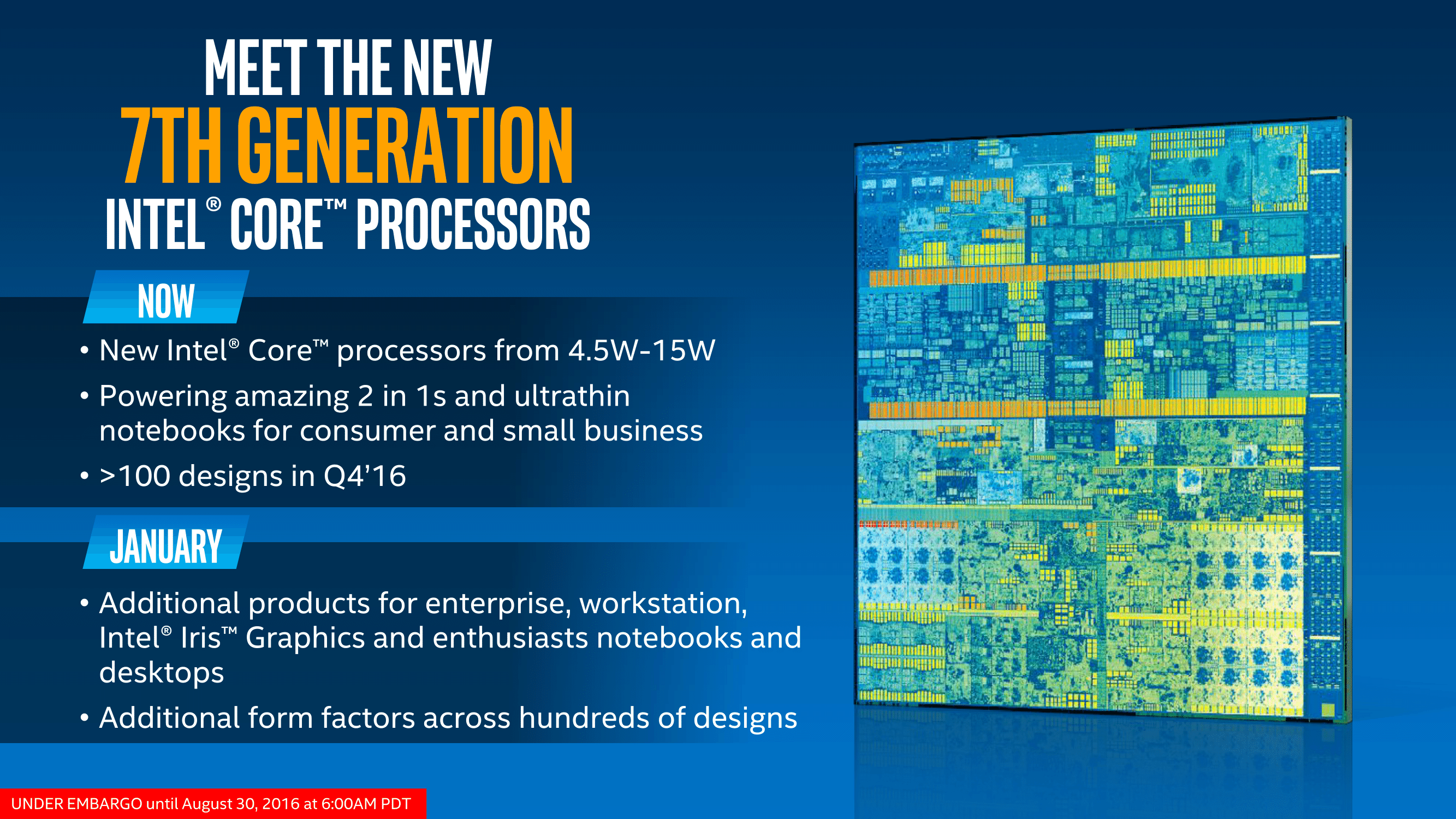

Today’s Announcement

The reveal today covers several aspects of Kaby Lake. First is the actual SKUs that will be launched, which consist of three Kaby Lake-Y parts around 4.5W aimed at high-end tablets and 2-in-1 devices and three Kaby Lake-U parts at 15W for notebooks. Both sets of KBL-Y and KBL-U CPUs will feature in mini-PCs as well, so we expect to see the usual array of Zotac and ECS announcements in due course. We have details on all six CPUs to give you, including the new Core M branding regime for the 4.5W family of parts.

The pre-briefings we have had go into some detail regarding changes in the processor, particularly regarding the new enhanced media blocks inside the GPU to support new encode/decode features. The graphics power, in terms of EUs or the microarchitecture, hasn’t changed but the fixed function hardware has some nice upgrades for an updated version of Gen 9 graphics aimed at the upcoming era of 4K support. Ganesh has gone into detail for us over what that means, especially where power and battery life is concerned for anyone creating/consuming 4K content.

Kaby Lake also has an updated Speed Shift package, to accelerate the work already done with Skylake in boosting the performance of the CPU quicker to save power. Intel call it a refinement in the mechanism of handing frequency control back from the OS to the CPU, however ‘Speed Shift v2’ is an adequate moniker to show the upgraded difference.

Intel hasn’t gone into much detail regarding the new 14nm+ process itself in terms of specifics, but has listed a number of performance gains that come out of the new CPU. The fundamental microarchitecture between Skylake and the new Kaby Lake parts is practically unchanged (DMI 3.0 now allows PCIe 3.0 x4 NVMe drives from the integrated PCH), but the updated fin profile and reduced ‘strain’ by the larger fin pitch is being quoted as giving a 12% performance increase due to process alone, typically through additional frequency for the same power. The main benefits to KBL will be in that frequency due to the 14nm+ process as well as the new media capabilities.

As always, Intel consistently emphasizes the difference between a new notebook/2-in-1 based on a 15W Kaby Lake processor compared to a 5-year old device, such one based on a mobile Sandy Bridge ULV part. Intel continually sees its market revolving around new experiences created by new form factors, and to generate revenue requires people to upgrade and decide how these new experiences can influence an upgrade. Intel expects to have over 100 Kaby Lake system designs in the consumer channel by Q4, including 120+ using Thunderbolt 3, 100+ using Windows Hello (either via a Real Sense camera or a fingerprint sensor), 50+ designs with 4K UHD as a primary feature and 25+ designs with contact enabled pens. Kaby Lake should be pin compatible with Skylake based designs, meaning that for a number of cases we will simply see a drop in, but others will have new design IDs on show.

129 Comments

View All Comments

lilmoe - Saturday, September 3, 2016 - link

I couldn't give a rat's bottom how cheap Intel's chips become. If AMD gets similar performance at reasonable prices, then good-bye Intel for me.BillBear - Tuesday, August 30, 2016 - link

Given the new 14nm+ process, is it safe to speculate that the original problem with 14nm that delayed the hell out of Broadwell and outright killed some of the desktop versions of Broadwell was a power leakage problem?saratoga4 - Tuesday, August 30, 2016 - link

I don't think leakage was a huge problem. Yields appear to have been though. Intel has some slides explaining that they ramped slower than expected.Jumangi - Tuesday, August 30, 2016 - link

So possibly no real IPC gains in the desktop version? No point in waiting if your looking to upgrade then.wumpus - Tuesday, August 30, 2016 - link

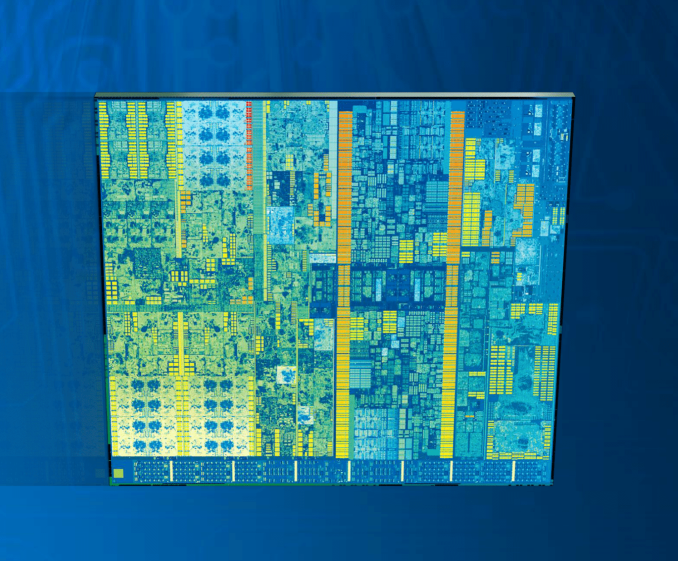

Not for this. I keep looking at that die photo and wondering how hard it would be to replace some of that silly graphics bit with 2-4 cores. Maybe they will do it once zen ships. Maybe it would generate too much heat and won't work (I suspect the big multicore jobs have more cache/core area than these chips have (GPU+cache)/core). Maybe Intel will someday include a pony.Molor - Tuesday, August 30, 2016 - link

They kind of do that. They call it the extreme version and charge more for it. Graphics nodes tend to be more forgiving of flaws due to redundancy. AMD and NVidia usually disable a broken SM or two per chip for yields. It would be interesting to know if Intel does the same.shabby - Tuesday, August 30, 2016 - link

Pretty much, the 12% benchmark increase came from a 13% clock bump, same wattage though apparently.someonesomewherelse - Thursday, September 1, 2016 - link

Are you talking about single thread IPC or total chip? I think that single thread IPC improvements are going to (or already have) become too expensive for most applications and without programmer/compiler help. Things that vectorize well are probably the last area where large improvements are realistic. But this will either require great programmers that can actually utilize current (AVX2) and future SIMD instructions in their code + higher development costs or dropping support for older cpus (neither sounds good). Per chip IPC is probably easier but you still need good programmers/compilers or the use of multiple expensive applications at the same time (why not play a game while encoding 3 videos.... with enough cores/threads/cache/memory bw/io b this would work) .Clocks could still be increased if you are willing to accept high power consumption and expensive cooling.

However unless Zen is an extreme success Intel has no reason to do this since slow and expensive increases are more profitable and they have no reason to do this.

akmittal - Tuesday, August 30, 2016 - link

Any chance to see these in this year's macbook lineup.lilmoe - Tuesday, August 30, 2016 - link

As much as I dislike Apple's ways, sometimes they do things for a reason.1) Apple seems very hesitant to bother with Skylake because the various problems/bugs associated with the new architecture. It seams that Haswell/Broadwell is doing the job good enough for them and the "new features" aren't worth it in their general assessment. Macbooks are more media consumption/creation-centric and they're probably waiting on the new fix-function features.

2) Cost and profitability. If the above is true, it makes sense to stay with Haswell/Bradwell to maximize profit. Just like how they're using 3 gen old AMD graphics.

3) Lower than expected demand? Not so sure, but possible.

4) And I'm being hopeful here: *Zen* (and future HBM APUs). Keller has a history working "with" Apple, and they actually like his designs which play well with their OS(s). I'm being hopeful because Apple's marketing prowess and branding may be the beacon AMD (and the competitive market) needs to unleash the new platform and drive Intel to a corner forcing them to lower prices.