AMD Reiterates 7nm Roadmap: Navi, Matisse, & Rome to Launch in Q3

by Anton Shilov on May 17, 2019 8:00 AM EST

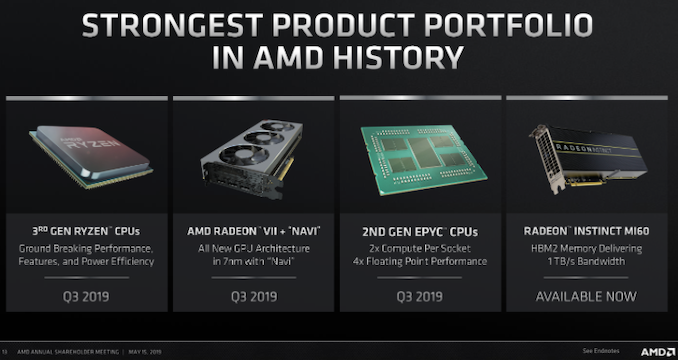

AMD this week held its Annual Shareholder Meeting where it reiterated its current technology roadmap and once again confirmed that that its major products set to be released this year based on 7nm will be formally introduced in Q3. Previously the company implied on launch timeframes of its Navi GPU (at least one of them), Matisse CPUs, and Rome server CPUs, but never made a firm promise about the third quarter - this announcement is a commitment to delivering these products in Q3.

The High Level

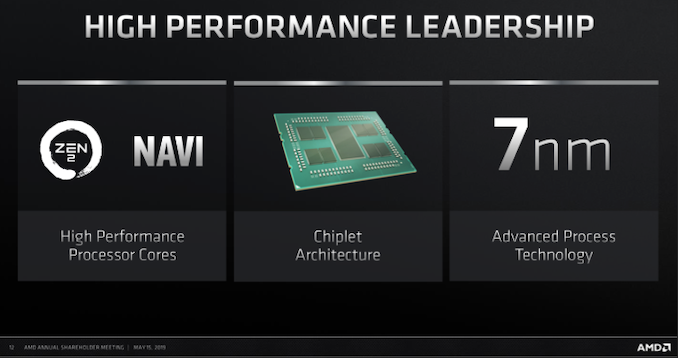

On a high level, AMD believes that there are four technology pillars that will define its product roadmap in 2019 and forward. These pillars are: the Zen 2 CPU microarchitecture, its Navi GPU architecture, chiplet-based design architecture that enables it to mix and match features and technologies to build a right processor for a given platform, and IP for TSMC’s 7 nm manufacturing technology.

Since R&D processes take years, it was crucial for AMD to make the correct bets when its comes to microarchitecture and fabrication process. That said, this year’s product launches represent a culmination of multi-year efforts by the whole company, but considering that numerous architectural things may be re-used for years, it is important that they have been developed and implemented.

The Products

AMD’s 3rd Generation Ryzen processor, known as Matisse, promises a significant performance increase in general-purpose tasks from where AMD is today. It also adds several new features, such as PCIe 4.0 interface support. Launching this product “shortly in Q3” means that the company wants to make it available already during the important back-to-school season and well ahead of critically important holiday sales season.

Another vital product series for AMD is its next-gen lineup of GPUs based on its Navi architecture. At least one of these graphics processors will be launched in the third quarter. What is noteworthy is that Navi GPUs will coexist with AMD’s Radeon VII graphics cards, which indicates that the latter will continue to serve the enthusiast segment of the market. Furthermore, AMD’s 7nm Vega GPU in the form of the Radeon Instinct MI60 will continue to be offered for high-performance computing workloads.

Also due in Q3 are AMD’s 2nd Gen EPYC processors, known as Rome. These server CPUs are set to feature up to 64 cores powered by the company’s Zen 2 microarchitecture. It is worth keeping in mind that it takes server users some time to adopt new CPUs, and the launch of AMD’s 2nd Gen EPYC in Q3 does not necessarily mean that these processors will be used by a massive amount of designs straight away. Nonetheless, it is still important to release them rather sooner than later in a bid to ramp them up as soon as possible.

One product family worth mentioning is Threadripper. AMD's high-end desktop platform, currently available at 8-32 cores, is expected to be encroached on by the Ryzen 3000 series. AMD briefly held in its roadmaps that Threadripper based on Rome would be coming in 2019, however in its most recent disclosures, that commitment has no longer appeared and AMD has not commented on the matter. It could be that someone made a mistake putting it on the singular slide deck in which it appeared, or there's a level of inconsistency between AMD's presentation teams based on what they are presenting to whom. Hopefully AMD will clarify the matter in due course, and with Computex coming in two weeks, it would be a perfect time to do so.

Related Reading:

- AMD To Host “Next Horizon Gaming” Event & Product Unveil at E3 2019: June 10th, 3pm PT

- AMD: 7nm ‘Navi’ GPU & 'Rome' CPU to Launch in Q3

- AMD's 7nm CPUs & GPUs To Be Fabbed by TSMC, on Track for 2018 - 2019

- AMD Tech Day at CES: 2018 Roadmap Revealed, with Ryzen APUs, Zen+ on 12nm, Vega on 7nm

- AMD Unveils GPU Architecture Roadmap: After Polaris Comes Vega

Source: AMD

55 Comments

View All Comments

peevee - Friday, May 17, 2019 - link

"Isn't every company's product portfolio the strongest in its companies' history?"No, because strength is measured against competitive landscape.

Lord of the Bored - Saturday, May 18, 2019 - link

Honestly, I think it is hyperbolic overstatement. I'd argue the K8 era was probably AMD's strongest historical portfolio, because they were at a high point while the competition was at a low point.On the other hand, I admit that they didn't have a very BROAD portfolio at the time.

Ryzen is, taken in isolation, very nice. Navi is, in isolation, probably very nice(I certainly hope it is, anyways). But they don't exist in a vacuum. They're up against very strong competition from Intel and nVidia, both technologically and marketing-wise.

peevee - Friday, May 17, 2019 - link

The main interest in Threadripper for me is 4 memory channels instead of 2. As far as I understand, it would not be hard to do with chiplet design at all. Their Am4 socket probably does not support 4 channels, am I right?What I want is the new socket design with SODIMM slots ON ITS 4 SIDES (oriented parallel to the board), each on its own channel, to minimize distance (and so latency and voltage required) and maximize bandwidth. MB design will be greatly simplified too, as they'd only need paths for power and PCIe on the bottom, possible even in a dirt cheap 1-layer design.

Lord of the Bored - Saturday, May 18, 2019 - link

That actually makes a lot of sense.SO-DIMM in general makes a lot of sense, and I'm kinda confused why it hasn't made inroads in full-size systems. (I know, I know. Less room for DRAMs, requires more expensive, higher-capacity chips to reach the same capacities. Can still put two SO-DIMM slots in the same space as a single full DIMM. )

peevee - Monday, May 20, 2019 - link

For my specific proposal, SODIMMs are there because they are short enough to be put on all 4 sides of a socket without making the socket too large. The contacts should protrude into the socket from the sides, so the socket has contacts for CPU on the top and slots for SODIMMs on the sides, directly connected to the CPU (the best if the CPU package itself has memory contacts on its sides to shorten the paths further and simplify the socket itself).High throughput low latency memory might even make integrated GPU decent. Or eliminate the need for LLC.

mode_13h - Saturday, May 18, 2019 - link

For GPUs, it makes sense to have lots of channels. For CPUs, I don't know how much you'll really gain by cutting your channel width below 128 bits. Remember that most transactions are cacheline-sized (typically 64 bytes).Anyway, I have a suspicion they'll just program the Rome chiplets to route memory to the 4 enabled channels, on TR4 boards. Then, existing TR users can simply upgrade to a Rome CPU.

peevee - Monday, May 20, 2019 - link

"I don't know how much you'll really gain by cutting your channel width below 128 bits."I think it has already been cut a few CPU generations ago.

" Remember that most transactions are cacheline-sized (typically 64 bytes)."

Multiple cores typically require memory from different cache lines. And data required immediately is often 64 bits or less. So multiple smaller channels leave fewer cores idle waiting for data. Efficiency is not reduced as each channel can continue to read its own cache line if necessary.

mode_13h - Tuesday, May 21, 2019 - link

> I think it has already been cut a few CPU generations ago.Source?

> So multiple smaller channels leave fewer cores idle waiting for data.

It just means lower data rates (i.e. you have to wait longer for your data).

> Efficiency is not reduced as each channel can continue to read its own cache line if necessary.

What? I don't understand. Cache lines are filled by reading memory via a channel. The way you said it makes no sense to me.

Pinn - Friday, May 17, 2019 - link

Not even trying against nVidia.Korguz - Friday, May 17, 2019 - link

Pinnsays who ?? do you know how Navi will perform ? do you have links that show this ? seems most of it.. is still rumors and speculation