PCIe 6.0 Specification Hits Version 0.5: On Track for 2021

by Anton Shilov on February 21, 2020 10:00 AM EST- Posted in

- Interconnect

- PCIe

- PCI-SIG

- PCIe 6.0

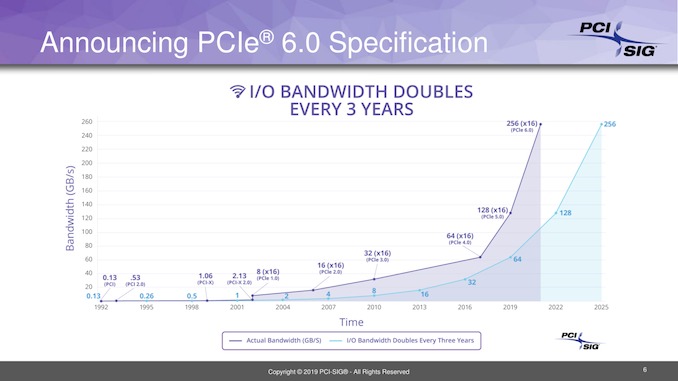

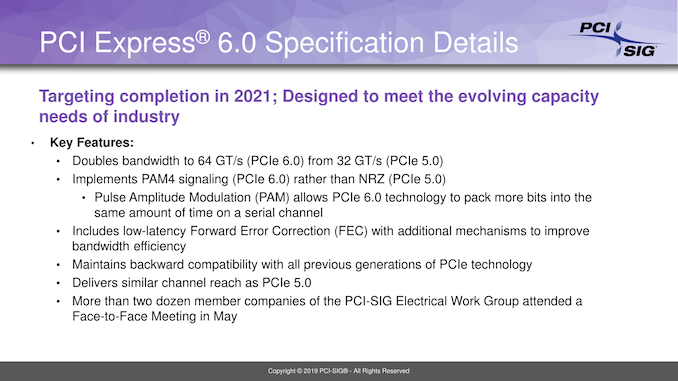

PCI-SIG has released version 0.5 of the PCIe 6.0 specification to its members this week. The new, "first draft" version of the spec includes the feedback the group got from its members after publication of version 0.3 back in October. With their latest update, PCI-SIG remains confident that it is on track to finalize the PCIe 6.0 standard in 2021.

It took PCI-SIG long seven years to complete the PCIe 4.0 specification, a long slog that the group has committed to avoiding going forward for PCIe 5.0 and beyond. With PCIe 6.0, PCI-SIG is keeping up that rapid pace of development, releasing the first draft version of the spec less than a year after formal announcement of the spec.

Overall, PCI-SIG has five key steps in creating a PCIe specification:

- Version 0.3 is beheld as a Concept and outlines the key features and architecture of the technology. In case of PCIe 6.0, we are talking about 64 GT/s per lane speed, pulse amplitude modulation with 4 levels (PAM-4) encoding, and forward error correction (FEC).

- Version 0.5 is considered as the First Draft specification and so it covers all the key aspects of the architecture and includes feedback from interested parties (within PCI-SIG) to version 0.3. Members of the group will be able to add new functionality to the technology at this point.

- Version 0.7 is deemed to be the Complete Draft, everything has to be defined at all levels and electrical specifications must have been validated via test chips. No new features may be added after release of this iteration of the specification.

- Version 0.9 is the Final Draft that is meant to allow PCI-SIG members to review the technology for their intellectual property.

- Version 1.0 is the Final Release.

The publication of version 0.5 of the PCIe 6.0 specification is essentially the final call for submissions of the new features by PCI-SIG member companies. Furthermore, with the first draft available, companies can start designing test silicon to ensure that everything works and even begin preliminary work on commercial chips.

The next milestone for the PCIe 6.0 specification will be the upcoming PCI-SIG Developers Conference 2020 in early June, where the group plans to present deep dives into the features of the technology.

Related Reading:

- PCIe 6.0 Dev Reaches v0.3; On-Track for a Full Specification In 2021

- PCI Express Bandwidth to Be Doubled Again: PCIe 6.0 Announced, Spec to Land in 2021

- Gen-Z PHY Specification 1.1 Published: Adds PCIe 5.0, Gen-Z 50G Fabric

- PCI-SIG Finalizes PCIe 5.0 Specification: x16 Slots to Reach 64GB/sec

- Synopsys Demonstrates CXL and CCIX 1.1 over PCIe 5.0: Next-Gen In Action

Source: PCI-SIG

74 Comments

View All Comments

mode_13h - Friday, February 21, 2020 - link

Yeah, PCIe is not a bus.Kevin G - Friday, February 21, 2020 - link

PCIe is not a shared bus, rather point to point. Only reason say a PCIe 3.0 device would down grade the performance of a PCIe 6.0 device is if something like the base clock is shared beyond how a controller bifurcates. Devices today handle mixing 4.0, 3.0, 2.0 and 1.0 devices rather well.romrunning - Tuesday, February 25, 2020 - link

Oh no, I was just reminiscing farther back, like in the early days of PCI (and even back in the days of ISA/EISA), not PCIe. You had some PCI components that would run at 33Mhz and some more advanced ones at 66Mhz, so you didn't want to accidentally slow down your 66MHz.romrunning - Tuesday, February 25, 2020 - link

Of course, don't quote me on the above - lots of things change over the years, including my memory! :)III-V - Friday, February 21, 2020 - link

The standard will be finalized next year... products won't come until much later.A5 - Friday, February 21, 2020 - link

Yep. Realistically we'll start to see PCIe 5 products in 2021.fred666 - Friday, February 21, 2020 - link

or maybe even 2022FreckledTrout - Friday, February 21, 2020 - link

Sure yes, server products. Going to be a closer to 2030 when you see desktop products.mode_13h - Friday, February 21, 2020 - link

I'm not sure it will ever reach the desktop.nandnandnand - Friday, February 21, 2020 - link

Do they eventually need photonics on the motherboard to improve speeds?