AMD Unveils Bulldozer & Bobcat: 2011 Microachitectures

by Anand Lal Shimpi on November 11, 2009 5:00 PM EST- Posted in

- CPUs

I spoke too soon. Earlier today I outlined AMD’s roadmap for 2010 - 2011. In 2011 AMD will introduce two next-generation microarchitectures: Bulldozer for the high end desktop and server space and Bobcat for the price/power efficient ultra mobile market. I originally said that AMD wasn’t revealing any more about its next-gen architectures, but AMD just proved me wrong as they unveiled the first block diagrams of both cores.

First up, Bulldozer. I hinted at the architecture in this afternoon’s article:

“A major focus is going to be improving on one of AMD’s biggest weaknesses today: heavily threaded performance. Intel addresses it with Hyper Threading, AMD is throwing a bit more hardware at the problem. The dual integer clusters you may have heard of are the route AMD is taking...”

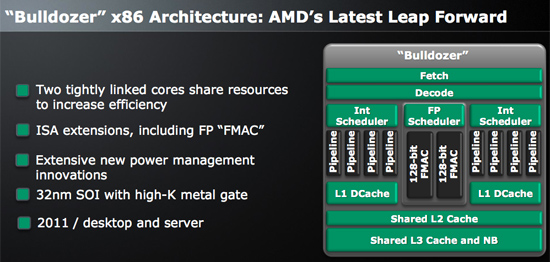

And here’s the block diagram:

Bulldozer: AMD's Latest Leap Forward, will it be another K8 to Intel's Sandy Bridge?

This is a single Bulldozer core, but notice that it has two independent integer clusters, each with its own L1 data cache. The single FP cluster shares the L1 cache of the two integer clusters.

Within each integer “core” are four pipelines, presumably half for ALUs and half for memory ops. That’s a narrower width than a single Phenom II core, but there are two integer clusters on a single Bulldozer core.

Bulldozer will also support AVX, hinted at by the two 128-bit FMAC units behind the FP scheduler. AMD is keeping the three level cache hierarchy of the current Phenom II architecture.

A single Bulldozer core will appear to the OS as two cores, just like a Hyper Threaded Core i7. The difference is that AMD is duplicating more hardware in enabling per-core multithreading. The integer resources are all doubled, including the schedulers and d-caches. It’s only the FP resources that are shared between the threads. The benefit is you get much better multithreaded integer performance, the downside is a larger core.

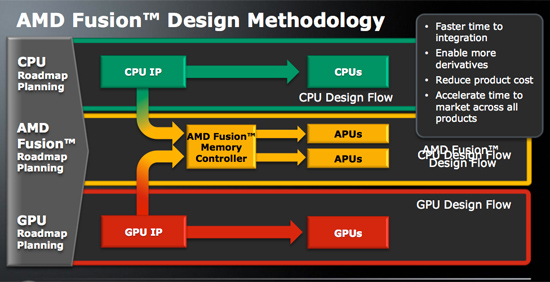

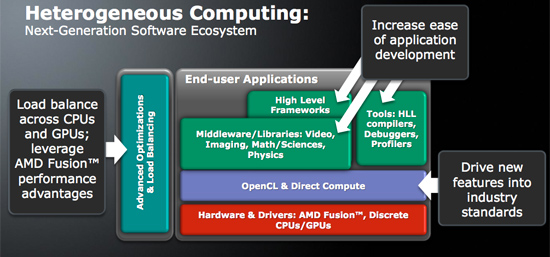

Doubling the integer resources but not the FP resources works even better when you look at AMD’s whole motivation behind Fusion. Much heavy FP work is expected to be moved to the GPU anyway, there’s little sense in duplicating FP hardware on the Bulldozer core when it will eventually have a fully capable GPU sitting on the same piece of silicon. While the first incarnation of Bulldozer, the Zambezi CPU, won't have an on-die GPU, presumably future APUs will use the new core. In those designs the Bulldozer cores and the GPU will most likely even share the L3 cache. It’s really a very elegant design and the basis for what AMD, Intel and NVIDIA have been talking about for years now. The CPU will do what it does best while the GPU does what it is good at.

Fascinating.

AMD’s Next-Generation Ultramobile Core: Bobcat

Next up is Bobcat:

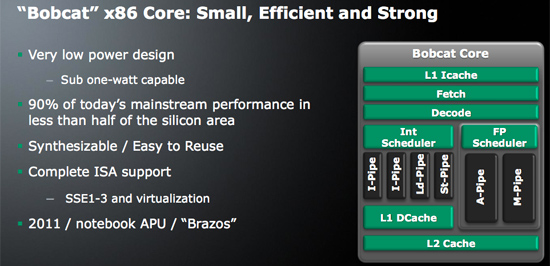

AMD says that a single Bobcat is capable of scaling down to less than one watt of power. Typically a single microarchitecture is capable of efficiently scaling to an order of magnitude of TDP. If Bobcat can go low as 0.5W, the high end would be around 5W. If it’s closer to 1W at the low end then 10W would be the upper portion. Either way, it’s too low to compete in current mainstream notebooks, meaning that Bobcat is strictly a netbook/ultraportable core as AMD indicated in its slides. Eventually Bulldozer will probably scale down to take care of the mainstream mobile market.

AMD provided very little detail here other than it delivers 90% of today’s mainstream performance in less than half of the silicon area. If AMD views mainstream as an Athlon II X2, then Bobcat would deliver 90% of that performance in a die area of less than 60mm^2.

Clearly this is bigger than Atom, but that’s just a guess. Either way, the performance targets sound impressive. SSE1-3 are supported as well as hardware virtualization.

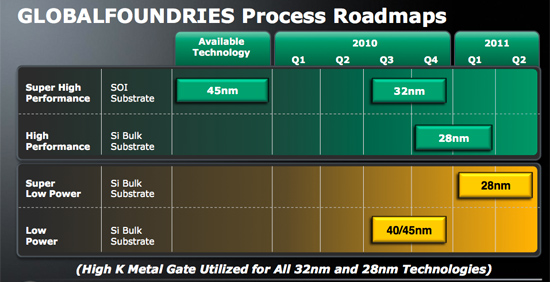

AMD wouldn’t tell me what process it would be made on but they did hint that Bobcat would be easily synthesizable. I take that to mean it will be built on a bulk 28nm process at Globalfoundries and not 32nm SOI.

Both of these cores will be out in 2011. We just need to make it through 2010 first.

68 Comments

View All Comments

eek2121 - Thursday, November 12, 2009 - link

Hi Guys, unfortunately, despite what this article implies, AMD is NOT targeting the high end with bulldozer. A quote from AMD's blog:" “Bulldozer” is AMD’s completely new, high performance architecture for the mainstream server, mainstream desktop and notebook PC markets that employs a new approach to multithreaded compute performance for achieving advanced efficiency and throughput. “Bulldozer” is designed to give AMD an exceptional CPU option for linking with GPUs in highly scalable, single-chip Accelerated Processing Unit (APU) configurations. "

Notice the use of mainstream in "mainstream server, mainstream desktop and notebook PC markets".

Will bulldozer be faster? Yes it will. Will it target high end/enthusiasts? No it won't. Enthusiasts will be using intel for the forseeable future unforunately.

Source: http://blogs.amd.com/unprocessed/tag/bulldozer/">http://blogs.amd.com/unprocessed/tag/bulldozer/

medi01 - Friday, November 13, 2009 - link

If the APU approach succeeds it will mean that we have CPU based on AMD + ATI expertise vs Intel + Intel's GPU. (even if Intel decides to buy nVidia, it will take time)Performance difference between AMD CPU and Intel CPU is much smaller, than between ATI GPU and Intel GPU. So I don't get, what would stop AMD from getting "top gaming performance" crown.

Risforrocket - Monday, November 16, 2009 - link

AMD's APU concept, as I see it, is a heterogeneous cpu which involves conventional cpu cores and gpu cores. The interesting but perhaps subtle point that needs to be looked at is that there is a trend in gpu design that is leading to a highly parallel floating point (don't know how to say it) graphics-like computing device that can be used for tasks other than graphics. This is exciting and if AMD does this right this can lead to a first strong step in new heterogeneous cpu architectures. This is the next step in the movement towards multi core cpu design.srp49ers - Friday, November 13, 2009 - link

I dont think Intel would be allowed to buy nvidia by regulators7Enigma - Friday, November 13, 2009 - link

TDP?fsdetained - Thursday, November 12, 2009 - link

You have no concept of business terminology do you?lifeblood - Thursday, November 12, 2009 - link

How will the CPU / GPU combo work? A low and CPU comes with the low end GPU on die, while the high end CPU comes with a high end GPU on die? Is this the end of discreet graphic cards? Or will you still be able to plug in a discreet card and it will work over PCIe as before?This is important for me as I tend to upgrade incrementally, a part at a time as I can afford it (and my wife doesn't notice it).

Also, will the first Bulldozer suck because it doesn't have the GPU on die? Will it try to use the discreet or IGP video card for FPU stuff at a horrible performance penalty?

Mr Perfect - Thursday, November 12, 2009 - link

The bulldozer slide says it's using a shared L2 cache. Does this mean L2 is shared between the two half-cores, or between two or more of the whole-cores?That particular slide doesn't make it clear where the core stops, and where the rest of the CPU(uncore?) begins. O_o

GaiaHunter - Friday, November 13, 2009 - link

It is shared between those 2 cores. I think AMD isn't calling them half-cores.Mr Perfect - Friday, November 13, 2009 - link

Hmm. I really wish they'd have shown off a block diagram of the whole CPU.The way it reads, it sounds like it will be 4 "cores", each with two smaller cores in it(what I called half-cores) making a total of 8 threads. I guess they don't want to show to much of their hand.