Understanding TLC NAND

by Kristian Vättö on February 23, 2012 1:14 PM EST- Posted in

- Storage

- SSDs

- OCZ

- Indilinx Everest

- TLC

A Brief Introduction to SSDs and Flash Memory

In almost every SSD review we have published, Anand has mentioned how an SSD is the biggest performance upgrade you can make today. Why would anyone use regular hard drives then? There is one big reason: price. SSD prices are still up in the clouds when compared to hard drive prices (especially before the Thailand floods) so for many, SSDs have not been a realistic option.

Forking over $700 for a 512GB SSD sounds crazy because a 500GB hard drive can be had for less than $50. Smaller capacities like 64GB and 128GB can already be bought for around $100 and $200 respectively, but unless you have the ability to have an SSD plus hard drive combo, such a small SSD doesn't usually cut it. If you have a desktop, the SSD + HDD combo should not be a problem but many laptops only have space for one 2.5" drive (unless you are willing to mod it afterwards by replacing the optical drive). SSD prices have been dropping for years now, but if the current rate continues it will take years before a $399 Walmart PC includes a reasonable size SSD. So what can be done?

Most of the time, SSD production costs are cut by shrinking the NAND die. Shrinking the die is the same as with CPUs: you move to a smaller manufacturing process, e.g. from 34nm to 25nm. In flash memory, this means you can increase the density per die and usually the physical die size is also smaller, meaning more dies from a single wafer. A die shrink is an effective way to lower costs but moving from one process to another takes time and the initial ramp of the new flash isn't necessarily cheaper. Once the new process has matured and supply has met demand, prices start to fall.

Since die shrinks are a relatively slow way to lower SSD prices and only contribute to steady reduction of prices, anyone looking to push higher capacity SSDs into the mainstream today will need something more. Right now, that "something more" is called Triple Level Cell flash, commonly abbreviated as TLC.

Rather than shrinking the die to improve density/capacity, TLC (like MLC) increases the number of bits per cell. In our SSD Anthology article, Anand described how SLC and MLC flash work, and TLC works the same way but takes things a step further. Normally, you apply a voltage to a cell and keep increasing it until you reach a point where the result is far enough from the "off" state that you now consider the cell as being "on". This is how SLC works, storing one bit per cell. For MLC, you store two bits per cell, which means instead of two voltage states (0 and 1) you have four states (00, 01, 10, 11). TLC takes that a step further and stores three bits per cell, or eight voltage states (000, 001, 010, 011, 100, 101, 110, and 111). We will take a deeper look into voltage states and how they work in the next page.

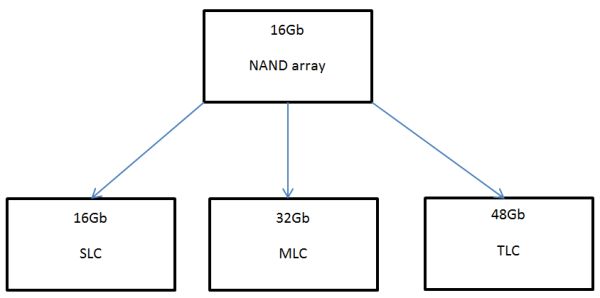

Even though SLC, MLC and TLC operate the same way, there is one crucial difference. Lets take a look at what happens to a NAND array depending on the amount of data per cell. The image above is a NAND array with ~16 billion transistors (one transistor is required per cell), i.e. 16 gigabits (Gb). This array can be turned into either SLC, MLC, or TLC. The actual array and transistors are equivalent in all three flash types; there is no physical difference. In the case of SLC flash, only one bit of data will be stored in one cell, hence your final product has a 16Gb capacity. When you up the bits per cell to two (MLC), you get 32Gb because now you have two bits per cell and there are still 16 billion cells. Likewise, three bits per cell (TLC) yields 48Gb.

However, TLC is a horse of slightly different color in this case. Capacities usually go in powers of two (2, 4, 8, 16 and so on) and 48 is not a power of two. To get a number that is a power of two, the original NAND array is chopped down. In our example, the array must be 10.67Gb in order to be 32Gb with three bits per cell, but since that is the same capacity as an MLC die, what is the benefit? You don't get more storage per die, but the actual die is smaller because the original 16Gb array has been reduced to a 10.7Gb array. That means more dies per wafer and hence lower cost.

| Comparison of NAND Wholesale Prices | |||

| Cell Type | SLC | MLC | TLC |

| Price per GB | $3.00 | $0.90 |

$0.60 |

Prices provided by OCZ

The theoretical price advantage of TLC isn't as great as SLC versus MLC, but it's still significant. In percentage, that is over a 30% reduction. The main reason is that MLC provides twice the capacity when compared to SLC (2bits per cell versus 1bit per cell), whereas TLC provides only 50% more than MLC (3bits per cell versus 2bits per cell). In fact, the price difference between MLC and TLC is directly proportional. TLC die is 33% smaller than a similar MLC die and in the prices provided by OCZ, TLC is also 33% cheaper than MLC. In theory, SLC should follow this equation as well and be priced at $1.80/GB, but there's limited 2Xnm SLC out in the wild, making SLC significantly more expensive than MLC and TLC at this point.

The reality of the matter is a little less clear. TLC NAND today isn't all that much cheaper than MLC NAND, which has contributed to its relative absence in the consumer SSD space. There's also a lack of controller support and market interest, which contribute to the higher prices of course.

90 Comments

View All Comments

aguilpa1 - Thursday, February 23, 2012 - link

I feel all warm and technical inside.Taft12 - Thursday, February 23, 2012 - link

"However, there have been quite a few widespread firmware issues, such as SF-2281 BSOD and Intel 320 Series 8MB bugs"No list of SSD firmware cockups is complete without mentioning the Kingston V200 abysmal write performance:

http://forum.notebookreview.com/solid-state-drives...

The fact that they're handing out V+ left and right to those requesting RMAs suggests to me the problem will never get fixed.

dorion - Thursday, February 23, 2012 - link

I'm having trouble understanding why the density gain from TLC is only linear and not quadratic. It seems like the web is crawling with a bunch of articles today saying the SLC -> MLC -> TLC density gain is 16 -> 32 -> 48. It should be 16 -> 32 -> 64. Am I right? Or is there something I'm not getting? Is it part of the ECC like Gray code?Death666Angel - Thursday, February 23, 2012 - link

Huh?SLC = 1 Cell, 1 bit

MLC = 1 Cell, 2 bits

TLC = 1 Cell, 3 bits

You seem to think that TLC is 1 Cell, 4 bits, which it is not. Not sure why you would think that, though.

JarredWalton - Thursday, February 23, 2012 - link

It's simple multiples, not powers. SLC stores one bit per cell, MLC is two, and TLC is three. MLC is thus twice the capacity of SLC, but TLC is only three times the capacity, not four. The power of two increase comes in the number of states to check: SLC checks two (0/1), MLC checks four (00,01,10,11), and TLC checks eight (000, 0001..., 110, 111). If someone were to try and do QLC they would need to check sixteen states, endurance would really plummet, and performance would be worse as well.dorion - Thursday, February 23, 2012 - link

I cant believe I overlooked the difference between bits you can store and how high you can count with a certain number of bits.ionis - Friday, February 24, 2012 - link

That only proves it should go 16->32->64.1 bit - 2 states - 16 Gb

2 bits - 4 states (double the previous) - 32Gb

3 bits - 8 states (double the the previous) - should be 64Gb not 48Gb. I'm still confused how the author got 48Gb.

JMC2000 - Friday, February 24, 2012 - link

The number of bits per cell is not equal to the number of voltage states. I'm not very knowledgeable in how NAND is produced, but I think the increase in voltage states by x2 per bit may have to do with the need for differentiation to write/erase each bit.ionis - Friday, February 24, 2012 - link

The article explicitly states that the number of bits per cell is equal to the number of voltage states.JMC2000 - Friday, February 24, 2012 - link

Do you mean this paragraph?"Rather than shrinking the die to improve density/capacity, TLC (like MLC) increases the number of bits per cell. In our SSD Anthology article, Anand described how SLC and MLC flash work, and TLC works the same way but takes things a step further. Normally, you apply a voltage to a cell and keep increasing it until you reach a point where the result is far enough from the "off" state that you now consider the cell as being "on". This is how SLC works, storing one bit per cell. For MLC, you store two bits per cell, which means instead of two voltage states (0 and 1) you have four states (00, 01, 10, 11). TLC takes that a step further and stores three bits per cell, or eight voltage states (000, 001, 010, 011, 100, 101, 110, and 111). We will take a deeper look into voltage states and how they work in the next page."

Or this one?

"SLC only has two program states, "0" and "1". Hence either a high or low voltage is required. When the amount of bits goes up, you need more voltage stages. With MLC, there are four states, and eight states with TLC. The problem is that the silicon oxide layer is only about 10nm thick and it's not immortal; it wears out every time it's used in the tunneling process. When the silicon oxide layer wears out, the atomic bonds break and during the tunneling process, some electrons may get trapped inside the silicon oxide. This builds up negative charge in the silicon oxide, which negates some of the the control gate voltage."

Nowhere in the article does it state that the number of bits per transistor is equal to the number of voltage states.